TRANSISTORES DE EFECTO CAMPO

Los transistores más conocidos son los llamados bipolares

(NPN y PNP), llamados así porque la conducción tiene lugar gracias al

desplazamiento de portadores de dos polaridades (huecos positivos y electrones

negativos), y son de gran utilidad en gran número de aplicaciones pero tienen

ciertos inconvenientes, entre los que se encuentra su impedancia de entrada

bastante baja.

Existen unos dispositivos que eliminan este inconveniente en

particular y que pertenece a la familia de dispositivos en los que existe un

solo tipo de portador de cargas, y por tanto, son unipolares. Se llama

transistor de efecto campo.

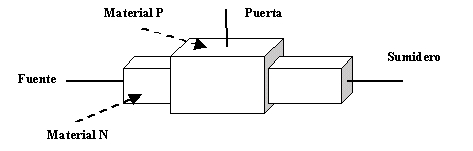

Un transistor de efecto campo (FET) típico está formado por

una barrita de material p ó n, llamada canal, rodeada en parte de su longitud

por un collar del otro tipo de material que forma con el canal una unión p-n.

En los extremos del canal se hacen sendas conexiones óhmicas

llamadas respectivamente sumidero (d-drain) y fuente (s-source), más una

conexión llamada puerta (g-gate) en el collar.

La figura muestra el croquis de un FET con canal N

Simbolos gráficos para un FET de canal N

Simbolos gráficos para un FET de canal N

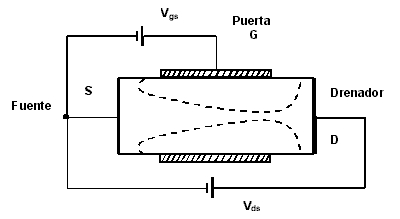

Disposición de las polarizaciones

para un FET de canal N.

La Figura muestra un esquema que ayudará a comprender el

funcionamiento de un FET. En este caso se ha supuesto que el canal es de

material de tipo N.

La puerta está polarizada negativamente respecto a la fuente,

por lo que la unión P-N entre ellas se encuentra polarizada inversamente y

existe (se crea) una capa desierta.

Si el material de la puerta está más dopado que el del

canal, la mayor parte de la capa estará formada por el canal. Si al tensión

de la puerta es cero, y Vds = 0, las capas desiertas profundizan poco en el

canal y son uniformes a todo lo largo de la unión.

Si Vds se hace positiva ( y Vgs sigue siendo cero) por el

canal circulará una corriente entre sumidero y fuente, que hará que la

polarización inversa de la unión no sea uniforme en toda su longitud y, en

consecuencia, en la parte más próxima al sumidero, que es la más

polarizada, la capa desierta penetrará más hacia el interior del canal.

Para valores pequeños de Vds, la corriente de sumidero es una

función casi lineal de la tensión, ya que la penetración de la capa

desierta hacia el interior del canal no varía substancialmente de su valor

inicial. Sin embargo, a medida que aumenta la tensión aumenta también la

polarización inversa, la capa desierta profundiza en el canal y la

conductancia de éste disminuye. El ritmo de incremento de corriente resulta,

en consecuencia, menor y llega un momento en que el canal se ha hecho tan

estrecho en las proximidades del sumidero que un incremento de Vds apenas

tiene efecto sobre la corriente de sumidero. Entonces se dice que el

transistor está trabajando en la zona de estricción (pinch-off), nombre cuyo

origen se evidencia en la figura anterior, llamándose tensión de estricción

Vp a la del punto de transición entre el comportamiento casi lineal y el casi

saturado.

Si a la puerta se le aplica una polarización negativa

estacionaria, la capa desierta penetra más en el interior que con la

polarización nula; por tanto, para pasar a la zona de estricción se necesita

menos tensión de sumidero. El aumentar la polarización negativa permite

tener la transición a la zona de estricción a corrientes de sumidero aún

inferiores.

El funcionamiento del FET se basa en la capacidad de

control de la conductancia del canal por parte de la tensión de puerta y, como la unión

puerta-canal se encuentra siempre polarizada inversamente, el FET es por esencia un

elemento de alta impedancia de entrada.

PARAMETROS DEL FET

La corriente de sumidero Id es función tanto de la tensión de sumidero Vds como de la

puerta Vgs. Como la unión está polarizada inversamente, suponemos que la corriente de

puerta es nula, con lo que podemos escribir:

Ig = 0 e Id = ƒ(Vds, Vgs)

En la zona de estricción (saturación) en que las características son casi rectas (en el

gráfico, son horizontales, pero en realidad tienen una pendiente positiva) podemos

escribir la respuesta del transistor para pequeños incrementos de Vds y Vgs en esta forma

El parámetro rd se llama

resistencia diferencial del sumidero del FET, y es la inversa de la pendiente de la curva.

Que como en el gráfico, dicha pendiente es cero (en la realidad, como he dicho antes

existe algo de pendiente), entonces la rd es infinita (muy grande).

El parámetro gm se le denomina

conductancia mutua o transconductancia, y es igual a la separación vertical entre las

características que corresponden a diferencias de valor de Vgs de 1 voltio.

|